文章摘要

制造先进逻辑芯片的过程始于电路设计,涉及从晶体管到系统设计的多层次步骤。设计图案通过电子束掩模写入设备(如可变形状束和多光束掩模写入机)被写入光掩模上。随后,在光刻曝光步骤中,掩模图案被缩小并投射到晶圆上的光刻胶层,再通过显影和蚀刻技术转移到基板。然而,光刻过程中由于光的衍射,图案会发生扭曲,导致图像保真度下降。为应对这一问题,光学邻近效应校正(OPC)技术被用于校正设计数据,以减少从设计到晶圆的误差。

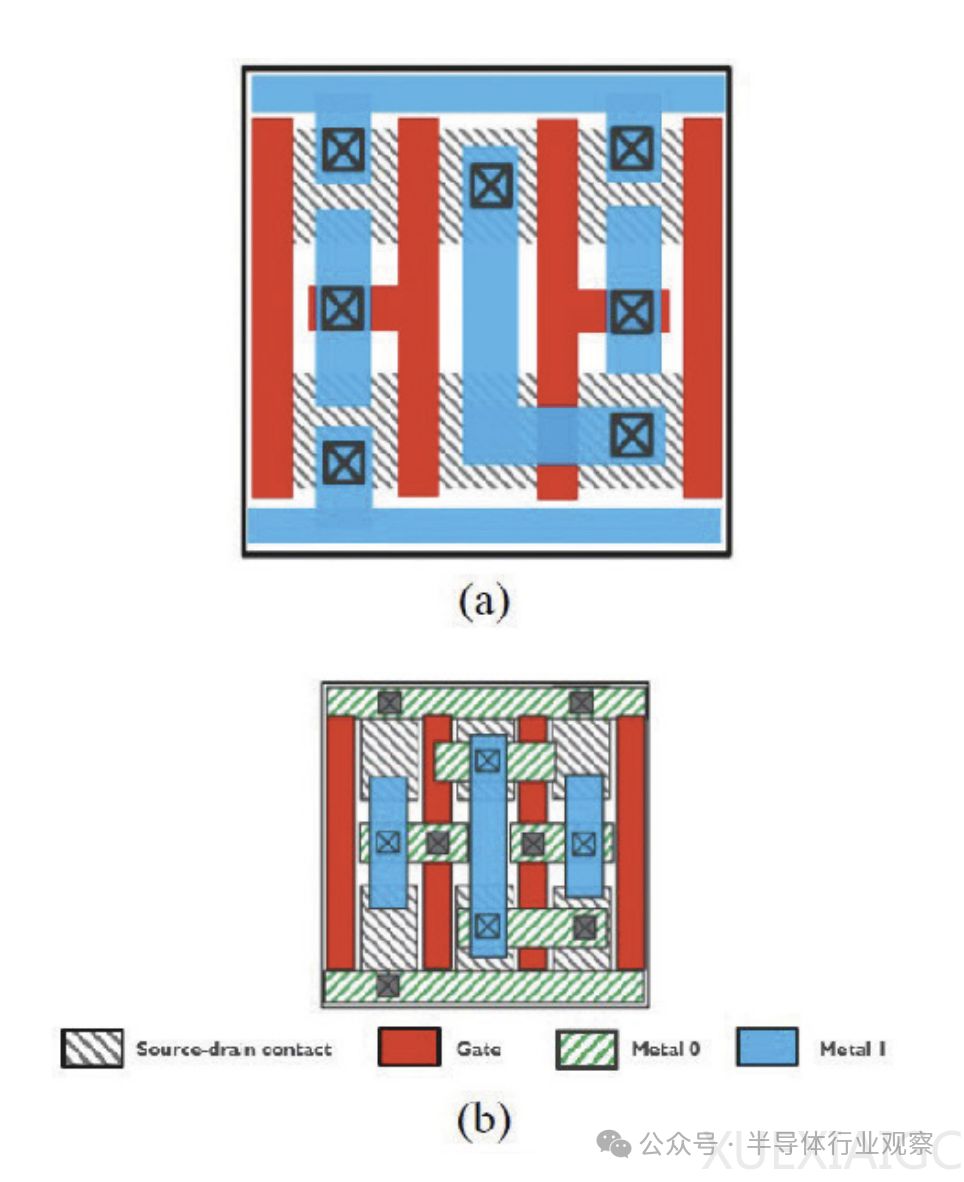

光刻、掩模和OPC技术的进步对提升逻辑芯片的功耗、性能、面积和成本(PPAC)至关重要。分辨率的提高通过缩短光波长或增加光刻扫描仪的数值孔径(NA)实现,例如从193纳米到193纳米浸没式光刻,再到极紫外光刻(EUV)和即将推出的0.55NA极紫外光刻(High NA EUV)。设计方面也随之发展,从2-D Manhattan布局转向关键层中的1-D Manhattan布局,以应对技术节点对间距微缩的要求。然而,1-D布局在电气连接时需要额外过孔层,增加了成本和电流路径长度。

尽管设计追求矩形结构,但掩模版和晶圆上的图案始终呈现弯曲状态,这是掩模写入器和光刻扫描仪工作方式的固有结果。为减少误差,业界开始探索在光掩模上写入曲线形状,多电子束掩模写入工具的出现促进了这一想法。此外,新型“曲线”OPC技术被提出,以改善光刻步骤的工艺窗口。曲线掩模和OPC技术已成为半导体行业的热门研发课题,并在2025 SPIE先进光刻和图形化会议上受到广泛关注。

imec提出在设计阶段引入曲线几何形状和路径的创新概念,其优势远超曲线OPC和掩模策略。曲线设计有望在降低晶圆制造成本的同时实现技术节点过渡,并提升电气性能。通过三个用例展示了其优势:首先,在标准单元和紧密间距金属层中采用曲线设计,可以减少金属层数量和过孔,降低晶圆成本并提升性能;其次,曲线形状连接源漏接触和栅极,可消除额外金属层,缩小单元面积并抑制成本;最后,曲线布局布线设计在标准单元上方的所有金属布线层中具有最大潜力,但需要更大的工业投入。

曲线设计的整体优势通过功率-性能-面积-成本(PPAC)品质因数体现,能够在不缩小尺寸的情况下实现技术节点进展,同时降低成本。然而,建立曲线设计面临挑战,包括精确表示曲线形状数据、控制数据量、建立专用设计规则和验证设计正确性。尽管存在这些挑战,曲线设计理念有望更高效地利用高数值孔径EUV光刻技术,并扩展低数值孔径EUV光刻技术的应用领域,如图像传感器、超透镜和汽车芯片。

曲线设计作为半导体行业的一项创新技术,有望彻底改变先进逻辑芯片的制造方式,推动技术节点的进一步微缩和PPAC性能的提升。

原文和模型

【原文链接】 阅读原文 [ 2728字 | 11分钟 ]

【原文作者】 半导体行业观察

【摘要模型】 deepseek-v3

【摘要评分】 ★★★★★